High speed 32Mbit MRAM for IoT microcontrollers

Renesas has detailed an embedded magnetic memory test chip with fast read and write operations built in a 22nm process.

The test chip includes a 32Mbit spin-transfer torque magnetoresistive random-access memory (STT-MRAM) cell array that achieves a 5.9ns random read access at a maximum junction temperature of 150°C, and a write throughput of 5.8Mbyte/s.

This is a key technology for microcontrollers uses as low power endpoint devices in the Internet of Things (IoT) with clock frequencies over 100MHz. Microcontrollers are moving to finer process geometries and the MRAM gives a cost advantage as it is built in the back end (BEOL) process rather than the flash memory built in the more complex and costly front end process.

Related STT-MRAM articles

- Emerging memory market is finding its direction

- Renesas develops write technologies for STT-MRAM

- Lower power MRAM targets for embedded designs

- Samsung uses MRAM for AI in-memory computing

- TSMC moves to MRAM for scratchpad memory

Renesas worked with a 22 nm process because it is compatible with existing CMOS logic process technology and requires fewer additional mask layers. However, MRAM has a smaller read margin than flash memory, which degrades the read speed. A large gap between the CPU operating frequency and the read frequency of the non-volatile memory is also a challenge since it can reduce the MCU performance.

MRAM can also achieve shorter write time than flash memory because it requires no erase operation before write operation. However, further speed improvements are needed to shorten system downtime for over-the-air (OTA) updates required for endpoint devices and reduce costs for end product manufacturers in writing control codes for MCUs.

The higher speed of the new design is key to tackling these challenges.

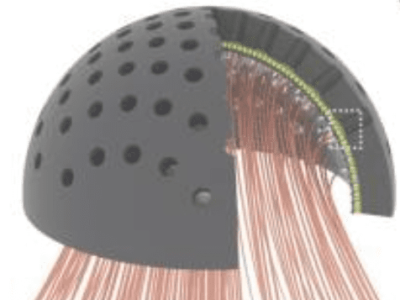

STT-MRAM uses memory cells including magnetic tunnel junction (MTJ) devices in which high and low-resistance states correspond to data values of 1 and 0 respectively to store information. A differential sense amplifier distinguishes between the two states by reading the voltage difference in discharge speed between the memory cell current and reference current. However, since the memory cell current difference between the 1 and 0 states is smaller for MRAM than for flash memory, the voltage difference read by the sense amplifier is smaller. Even if the discharge time is extended to wider voltage differences between the differential input nodes of the sense amplifier, both of the input nodes are susceptible to being completely discharged before securing a necessary voltage difference. This problem is particularly acute at high temperatures.

To resolve this issue, Renesas used capacitive coupling to boost the voltage level of the differential input nodes, allowing the differential amplifier to sense a voltage difference even when the memory cell current difference is small, achieving high-precision and fast read operation.

The design achieves the higher speed by shortening the mode transition time during write operation.

This divides up the areas to which write voltage is applied and, by inputting the write address before the write voltage setup, it selectively applies voltage only to the necessary area. This reduces the parasitic capacitive load on the area where the voltage is applied during the write operation, reducing the voltage setup time. As a result, the mode transition time to write operation is reduced by approximately 30%, speeding up write operation.

Other MRAM articles

- Startup raises $11m for spin SOT-MRAM

- MRAM revolution could trigger new ARM architecture

- MRAM could store data in nanoseconds

- imec makes spin-orbit torque MRAM on 300mm silicon

Other articles on eeNews Europe

- ARM battles RISC-V at Renesas

- D-Wave steps up battle for quantum computers

- The five biggest microcontroller suppliers in 2021

- Imverse raises $4.8m for live holograms on Zoom

- Achieving ISO/SAE21434 cyber security using Secure Flash

- First commercial unikernel with POSIX compatibility

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News