SDK, neural net IP ease low-power FPGA edge AI vision design

Part of the Microchip Smart Embedded Vision initiative, VectorBlox Accelerator SDK will help to provide power-efficient inferencing in edge applications by providing an easier route for software developers to implement algorithms in the company’s PolarFire FPGAs. The software provides the tools for developers to create low-powered and flexible neural network applications on Microchip’s PolarFire FPGAs without learning the FPGA tool flow. Instead, developers can implement power-efficient neural networks in C/C++.

The new tool kit can execute models in TensorFlow and the open neural network exchange (ONNX) format. ONNX has the ability to support frameworks including Caffe2, MXNet, PyTorch, and MATLAB. The VectorBlox Accelerator SDK is supported on Linux and Windows operating systems, and it also includes a bit accurate simulator to validate hardware accuracy while in the software environment. The neural network IP included with the kit allows the loading of different network models at run time.

PolarFire FPGAs can provide up to 50 percent lower total power than competing devices while offering 25 percent higher-capacity math blocks that can deliver up to 1.5 TOPS. FPGAs also have the flexibility to offer customization and differentiation through their inherent upgradability. They can also host many functions on a single chip.

More information

Related news

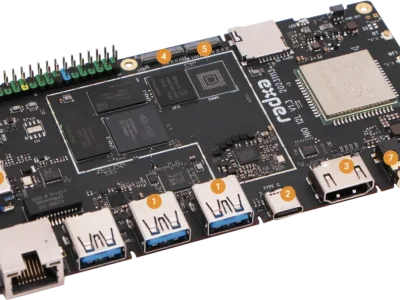

Embedded board uses both PolarFire and SmartFusion2 FPGAs

Signal routing software picks a path for T&M switch system development

The anatomy of a network switch: an eight-port, gigabit glitch

Aldec optimizes FPGA routing resources for power and performance gains

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News